如何使用"Cut and Stitch"定制生成快10倍的PCB和IC封装模型

作为经验丰富的SI专家,从抽象电路仿真到详细的3DEM分析,您可能会应用多个求解器和仿真器来完成高速设计任务。而且很多时候,您倾向于应用最详细、计算功能最强大的工具,以获得最准确的结果。缺点是,运行这些工具需要大量的时间。更糟糕的是,由于工具的设置问题,您可能会收到不好的结果。不幸的是,这样的结果还需等待几个小时甚至几天才出现。所有花费的等待时间都被浪费了。多么令人沮丧!

但是 – 我们为什么要忍受这样的挫折,只希望它永远不再发生…

其实,你有另一种出路?

Cut and Stitch

Brad Brim,DesignCon常驻专家,研究封装和电路板的信号和电源完整性应用,曾经也跟你们一样。他在职业生涯早期经历了这样的挫折,然后根据自己的经验避免了大部分问题,但即使是经验丰富的3D专家,偶尔也会成为牺牲品。正因为如此,他开发了一种新的方法,利用混合求解仿真流程以及“cut and stitch”方法,快速获得理想结果,一劳永逸。

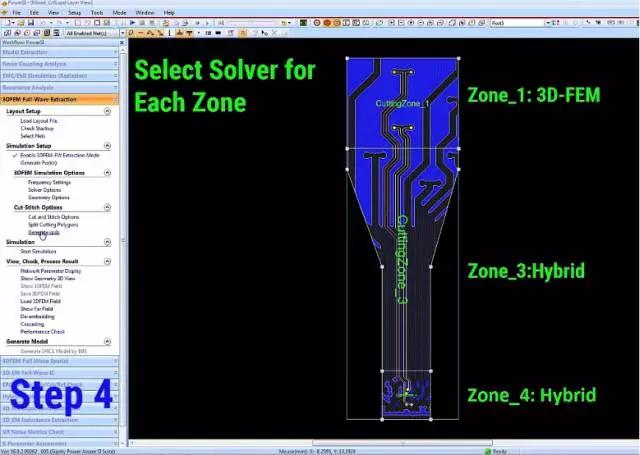

“cut-and-stitch”流程需要一个多边形边界来定义局部3D仿真的区域。然后通过简单地绘制切割线将该区域分割成“zones”。最后将每个zone的3D仿真结果组合起来得出一个综合的结果。尽管它可能使用频率不高,但这是我们可以灵活地为每个zone选择合适的3D求解器或混合求解器。

“cut-and-stitch”仿真流程的另一个便利之处在于可以从单个用户界面自动化驱动使用多个场求解器。这样可以显著节省时间和内存,并有助于以最少的工程时间确保精确的结果。

该技术的另一个功能包括,对你感兴趣的区域,使用匹配的场求解器,避免把3D全波分析时间耗费在过多的设计数据上。这种方法能够生成精确的互连模型。而在其它解决方案中需要花费更多的时间、并且问题可能未被如此战略性地解决。

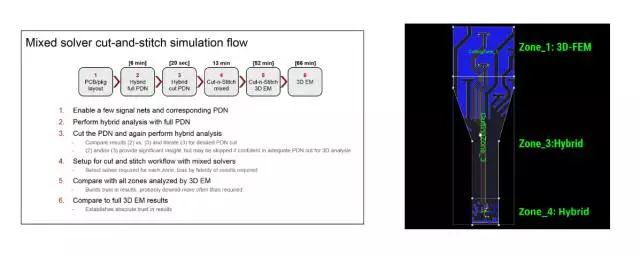

他绘制了混合求解器“Cut and Stitch”仿真流程的六个步骤(见下左图),并强烈推荐您不要跳过最初的两个混合求解器步骤。因为即使是对于最有经验的分析工程师,这两个初始步骤是以最小的时间投资(6分钟+20秒),来确保分析结果的成功、高效和准确。然后继续根据他指导您使用混合求解器cut-and-stitch的工作流程,提高成功率。在演示案例中,混合求解器的结果表明,电路板侧的过渡强烈的影响了电路的响应。该信息指导他仅选择那一区域进行3D全波仿真。(见下图)

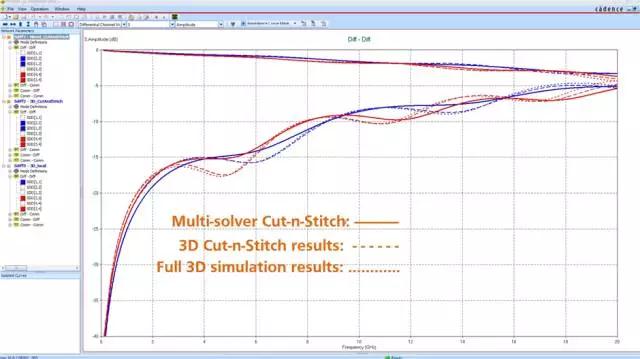

步骤4的13分钟cut-and-stitch仿真为此SerDes通道提供了精确的结果。 Brad Brim继续通过与全3Dcut-and-stitch仿真、完整(cut)设计(步骤6)中的全3D仿真的对比,来验证该方法。如下图所示,结果非常合理:

最后,Brad Brim总结道:“问题不在于是应用3D EM还是混合求解技术,而是如何更好地将两者结合起来应用。”