PCB?DFM分析

传统的PCB设计方法针对PCB可制造性是工程师通过人工去一条一条无遗漏的按照PCB设计指导书检查,避免在某个问题上犯错误,但由于设计难度和项目复杂度的提高,检查项积累的越来越多,DRC检查的负担也越来越重,单靠EDA设计工具已无法满足设计和加工的要求,工程师依然要面对反反复复的核对和检查,甚至于不惜成本等下次投板回来才能发现错误的一面。迪浩提供的智慧的PCB DFM分析工具可以让设计工程师摆脱常规设计要面对的各种检查列表(checklist),其中包括电气检查,PCB生产检查,组装检查,测试检查,总装检查等,保证设计一次成功,避免繁琐的手工检查校对过程。

PCB设计与工艺质量的要求

PCB设计者除了考虑电气设计外,还要结合工艺,组装,测试,生产等要求,才能满足最终的设计要求,主要考虑点如下:

- 工艺选择要求

- PCB叠层和尺寸要求

- 结构/拼板/辅助边要求

- 基准点要求

- 器件布局要求

- 走线和腐蚀要求

- 回流/波峰/压接/手插件等要求

- 孔径设计要求

- 阻焊设计要求

- 表面处理要求

- ICT自动测试要求

- 丝印设计要求

- 产品特性要求

- 工艺文件规范要求

- 其他特殊设计要求

DFx解决方案的主要运作方式为:输入(Input)à 分析(Analysis)à 输出(Output),也就是将所需的数据输入之后,进行DFM的相关分析,确认为Bug-free之后,再行输出为可供生产制造的数据,以确保生产顺畅、质量无虞,并能加速新产品导入的时间,减少试产次数、避免重复错误。

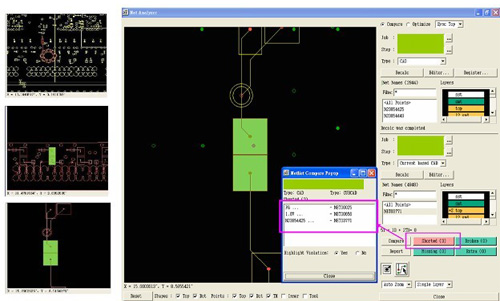

NetlistAnalyzer网表分析:

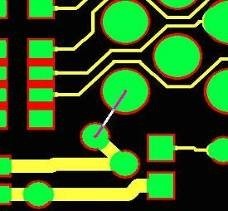

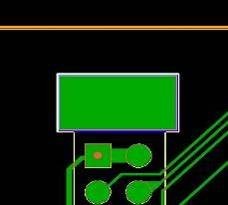

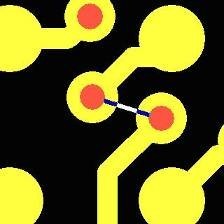

Netlist Analyzer使用实时核对之技术去截取实体线路的Netlist,再与来自CAD systems之Netlist做比对与分析。经过分析后以反映在实体之线路并过滤成"opens" 或 "shorts",提前在Gerber out之前便可避免额外成本。以下为范例:

其分析项目包括:

- RShorted Nets

- RBroken (Open) Nets

- RExtra Nets

- RMissing Nets

- RExtra Net Points

- RMissing Net Points

- RIsolated Plane Points

- RIntentional Shorts

- RIntentional Opens

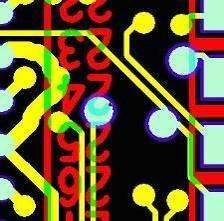

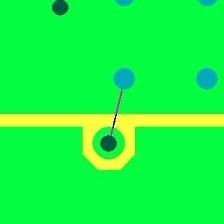

Assembly/Testability Analysis:

针对电子组装的潜在风险,提前在正式生产前找出制造方面的问题,提供事先修正的机会,以避免Rework,废板,墓碑效应等的资源浪费,此模块另可检查零件限高干涉的问题,分区域设定限高,避免机构组装的问题,同时,尚可分析测试点涵盖率,提供改善的依据,过去必须等到板子洗出来才能知道测试涵盖率,相当不经济,且修改又要再花时间,也无法确认是否正确,以此模块可大大改善此现象。

其分析包括六大项,共超过200个细项:

<Assembly/Testability Analysis>

- RFiducial Analysis

- RComponent Analysis

- RPadstack Analysis

- RTestpoint Analysis

- RSolderpaste Analysis

- RPin To Pad Analysis

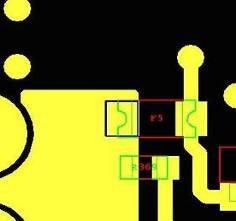

以下为部份检查项目的范例:

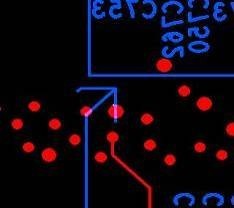

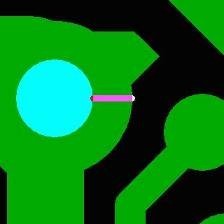

Fabrication Analysis:

此分析可提前分析PCB的可制造性,提供PCB厂可立即生产的Gerber数据,以避免来回确认所浪费的时间,以及PCB板厂疏忽所造成的质量问题,如文字重迭,多余的线路和钻孔,过去必须等到板厂回复才能知道问题,部分有经验的板厂会进行修改,但不见得会提供修改的项目,此为一潜在风险,必须有效避免。

此分析包括七大项,共超过200个细项:

- RDrill Checks

- RSignal Layers Checks

- R Power/Ground Checks

- RSolder Mask Checks

- RSilk Screen Checks

- RProfile Checks

- REtching Analysis

- RSMD Summary

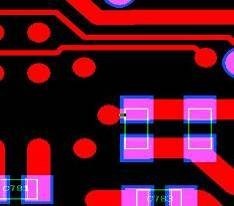

以下为部份检查的范例:

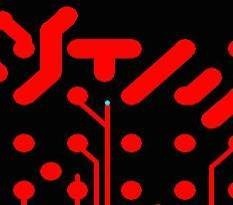

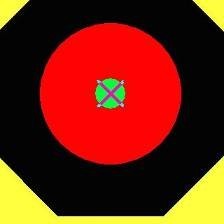

HDI Microvia Analysis (High Density Interconnect)

所谓的HDI就是利用微盲孔(Microvia)搭配细线与密距以达到高度互联的一种技术,其孔径在6mil以下、线宽/线距在3mil/3mil或更细更窄,HDI其最终目的就是在相同单位面积中能够搭载更多组件或是布更多的线路。

此分析包括三大项,共35个细项:

- RHDI Microvia Solder MaskChecks

- RHDI Microvia Signal Checks

- R HDI Microvia Drill Checks

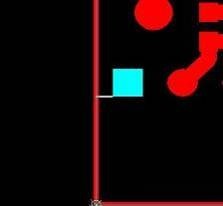

以下为部份检查的范例:

|  |

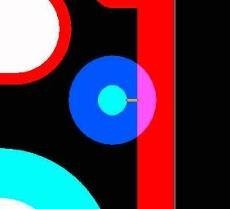

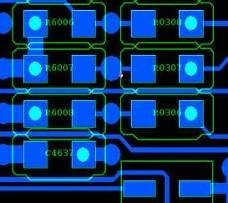

| 光学点下方走线恐造成SMT定位误判 | RA32的Pin脚左右两边距离不正确 |

|  |

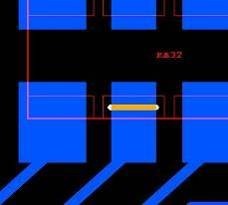

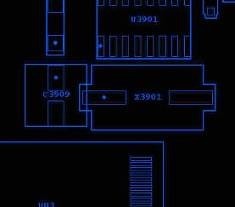

| C3909 & X3901之间已经互相重迭干涉, SMT无法置件 | 测试点太靠近零件R0307, 恐造成测试的干涉 |

|  |

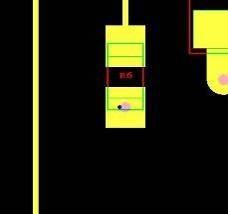

| SMD零件PAD底下有钻孔, 恐造成焊锡不良 | 板底SMT零件离DIP孔太近,会造成波峰焊之少锡或焊锡不良 |

|  |

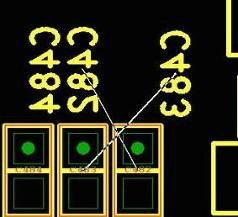

| 零件之位置序号摆放错误,文印数据与CAD不同,造成生产线OP混淆,如C482 & C483 | 测试点和测试点靠太近,造成测试时的干涉 |

|  |

| 未盖绿漆的via和零件pad靠太近,可能造成锡丝 | 考虑测试机台的限制,测试点不能靠折断边太近 |

|  |

| 测试点被文印层覆盖,可能造成接触不良而误判 | SMD PAD没有钢板开孔数据, 恐造成钢板漏开 |

|  |

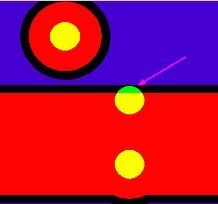

| 2 pin零件, 若两pad的接铜比例差异过大, 易造成零件一边翘起, 造成所谓的墓碑效应 | Pad与Pad间没有开防焊 (开天窗) |

Fabrication Analysis:

此分析可提前分析PCB的可制造性,提供PCB厂可立即生产的Gerber数据,以避免来回确认所浪费的时间,以及PCB板厂疏忽所造成的质量问题,如文字重迭,多余的线路和钻孔,过去必须等到板厂回复才能知道问题,部分有经验的板厂会进行修改,但不见得会提供修改的项目,此为一潜在风险,必须有效避免。

此分析包括七大项,共超过200个细项:

- RDrill Checks

- RSignal Layers Checks

- R Power/Ground Checks

- RSolder Mask Checks

- RSilk Screen Checks

- RProfile Checks

- REtching Analysis

- RSMD Summary

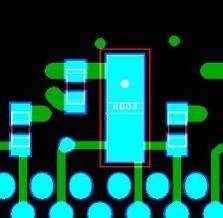

以下为部份检查的范例:

|  |

| 零件R4001在文字层没有位号标示, 恐造成OP工作上的错误 | 文印数据重迭,字跟字,或字跟线,造成生产线人员不易读取文印数据 |

|  |

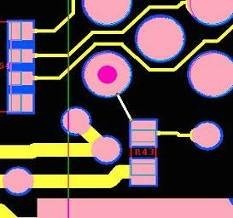

| 同个讯号彼此太过靠近, 恐造成细丝, 影响信号质量 | 同个讯号彼此太过靠近, 恐造成细丝, 影响信号质量 |

|  |

| 测试点的防焊未开,测针无法接触到铜面 | 文字和PTH孔已重迭 |

|  |

| 文印数据重迭,字跟字,或字跟线,造成生产线人员不易读取文印数据 | 脖子线恐造成信号质量问题 |

|  |

| Soldermask太靠近信号, 恐造成短路 | 文字与孔重迭, 会被钻掉 |

|  |

| 空接线, 该线段无实际作用 | 焊盘间存在许多小碎片, 恐因光绘片松动或腐蚀液聚集造成铜片剥离,使电路功能失效 |

|  |

| 重复钻孔 | solder mask与外层pad的annular ring距离太近 |

|  |

| 中间那颗导通钻孔会因两pad的间距太小而造成无法导通 | 指原始与铜面连接的钻孔, 加大etch shrink值后, 造成钻孔未与铜面连接 |

|  |

| 加大etch shrink值之后所产生的一些碎铜 | 因两区域间的导通距离只有1.8mil, 故放大etch shrink值后, 即造成两区域断路 |

|  |

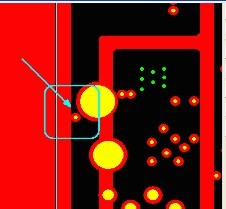

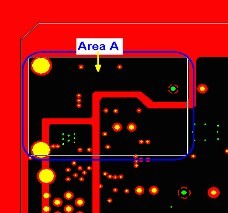

| Broken Contact结果报出两个区域Area A及Area B. 表示此两区域有断路的可能 | |

HDI Microvia Analysis (High Density Interconnect)

所谓的HDI就是利用微盲孔(Microvia)搭配细线与密距以达到高度互联的一种技术,其孔径在6mil以下、线宽/线距在3mil/3mil或更细更窄,HDI其最终目的就是在相同单位面积中能够搭载更多组件或是布更多的线路。

此分析包括三大项,共35个细项:

- RHDI Microvia Solder MaskChecks

- RHDI Microvia Signal Checks

- R HDI Microvia Drill Checks

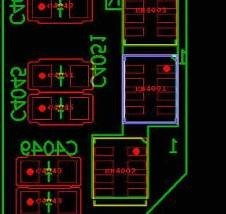

以下为部份检查的范例:

|  |

| Via孔的防焊层漏开,将导致该via内进绿漆,造成拒焊 | Via孔的防焊层只开部分,将导致该via内进绿漆,造成拒焊 |

|  |

| 两Via孔距离太近,可能造成渗镀,微short。 | Via孔的孔环太小,可能使该via孔破 |

|  |

| Pad与PTH/NPTH孔重迭,造成该pad被孔钻掉 | Via孔与PTH孔距离太近,可能造成渗镀,微short。 |