| 序号 | 标题 | 更新时间 |

|---|---|---|

| 1 | CMS?Yeptools PCB-设计功能增强以及工艺审查模块 | 2019-09-20 |

CMS??Yeptools?PCB-设计功能增强以及工艺审查模块

该模块基于AXL-Skill脚本语言开发,与Cadence工具菜单无缝集成,实现在PCB设计环境的初始化,快捷布局布线设定,约束环境定义、电气规则检查和DFX工艺规则在线分析检查,输出检查报告。

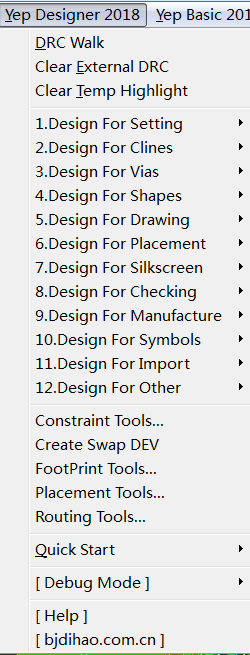

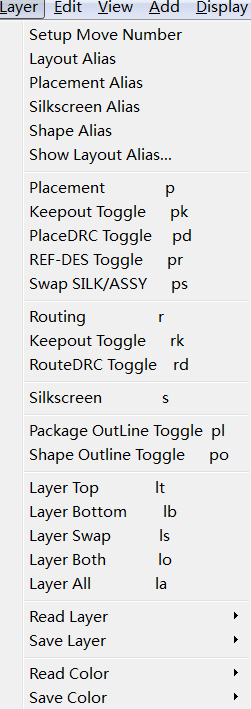

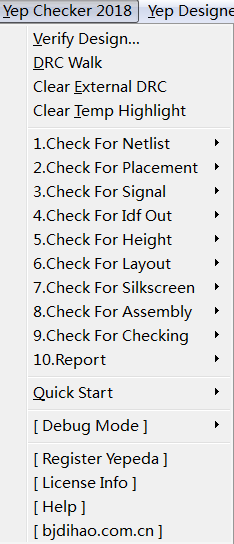

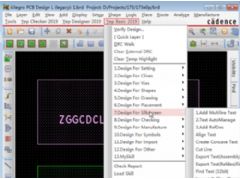

软件界面:

软件安装完成后,分为Yep Designer、Layer、Yep Checker三部分。

Yep Designer/Layer快速设计定义和输出

配置建立封装库的初始化的建库环境,包括设计单位,显示颜色,字体大小,标注等。配置建立电路板的初始化的设计环境,包括板子的详细设计叠层,显示颜色,设计规则,自动化正确识别电源信号,时钟信号,差分信号等。通过使用Yep Tools skill的快速设计环境配置模块,工程师可以一键实现封装库的设计环境的配置和电路板设计环境的配置。做到高效,准确度高,人工的干预少。

- 设计增强型,按照用户习惯和设计流程优化EDA设计工具菜单和功能,最大化提高设计效率。

- 支持一键公/英制转换

- 支持设计环境快速初始化,如颜色,层定义,快捷键定义

- 支持快速打开显示所有层和设定

- 支持网表对比

- 支持核对器件为何无法正常摆出

- 支持增加器件焊盘的引脚号

- 支持过孔对齐

- 支持丝印对齐

- 支持网表转换和文件加密

- 支持智能导入导出

- 支持Line/Cline转换为shape等

- 支持改变过孔网络名称

- 支持所有设置智能一键更新

- 支持叠层、颜色、格点、环境变量参数化自动设置。

- 支持自动包地,自动调整丝印,自动标注…等等。

- 初始化版图的图面大小,仅适用于新的项目开始设计的时候,快速的设定版图的图面大小。

- 用模块的走线结果,以便于将该走线结果复制到其他类似的模块。

- 批量改变走线的线宽。同时可以显示单一层面的线宽最大值与最小值。

- 手动切割铜线。执行命令,对矩形框选区域丝印线进行切割。

- 实现将铜线更改为铜皮。更改后的铜皮与铜线一样的层面。

- 多余走线线段和多余过孔的自动删除以及更改过孔网络信号名称。当然,这些功能现在已经全部包含到Yep Checker程序里面了,这个程序就不常用了。

- 提供走线在单层的Clines长度报告。注意:只提供选中的Clines长度,而不是整个网络长度。

- 提供与焊盘连接的走线宽度和铜皮宽度的总和报告。

- 针对选择的过孔进行网络名称更改。

- BGA封装芯片走线FANOUT扇出。

- 针对选择的过孔进行过孔类型替换。

- 针对矩形选择区域的铜皮进行切割。

- 将丝印Line或者丝印Text或者丝印Shape的class和subclass更改为任意的class和subclass。

- brd版图设计环境下,实现对symbol与symbol之间,pin与pin之间,text与text之间,对齐功能,包括上、下、左、右、中间方向。均衡分布功能,包括水平方向,垂直方向。在dra封装库设计环境下,实现对pin与pin之间的对齐功能和均衡分布功能。

- 移动高亮的器件到PCB板框的右下角。

- 在brd版图环境下,可以一次性精确定位器件的X轴坐标,Y轴坐标,旋转角度,固定信息,层面。可以输入REF,点击“Find”按钮查找器件。

- 批量进行丝印的字体大小、丝印字体的原点位置,丝印与器件相关的位置。

- 一次性增加多行文字

- 恢复被误删除的器件的REF丝印文字。有时候器件的REF丝印文字被误删除,可以使用该功能进行恢复。

- 检查REF方向是否和器件方向一致,主要用于常规电阻和电容等小器件的检查。也就是当器件是横着摆放的时候,REF方向也要求要横着摆放。当器件是竖着摆放的时候,REF方向也要求要竖着摆放。

- 相似模块的丝印摆放结果的复用。

- 导出Silkcreen层的REF和Line丝印坐标。

- 导入Silkcreen层的REF和Line丝印坐标。

- allegro 15.x系列丝印审核程序。

如何设定建库的环境为MM公制单位

如何在dra建库环境下如何设定快捷键

如何增加Allegro封装库的信息标识

如何设定Allegro dra建库环境下的快捷键

YepTools2018免费学习版下载地址及小视频链接观看地址

如何实现allegro brd版图文件版本从17.2降低到16.6

如何在Allegro中实现阴字体

CMS?Yeptools PCB-设计功能增强以及工艺审查模块

该模块基于AXL-Skill脚本语言开发,与Cadence工具菜单无缝集成,实现在PCB设计环境的初始化,快捷布局布线设定,约束环境定义、电气规则检查和DFX工艺规则在线分析检查,输出检查报告。

-

2019-09-20

CMS?Yeptools PCB-设计功能增强以及工艺审查模块

CMS?Yeptools PCB-设计功能增强以及工艺审查模块

-

2019-07-03

如何在Allegro中实现阴字体

如何在Allegro中实现阴字体

-

2019-07-03

如何实现allegro brd版图文件版本从17.2降低到16.6

如何实现allegro brd版图文件版本从17.2降低到16.6

-

2018-06-14

YepTools2018免费学习版下载地址及小视频链接观看地址

YepTools2018免费学习版下载地址及小视频链接观看地址

-

2018-07-30

如何设定Allegro dra建库环境下的快捷键

如何设定Allegro dra建库环境下的快捷键

-

2018-07-30

如何增加Allegro封装库的信息标识

如何增加Allegro封装库的信息标识

-

2018-07-30

如何在dra建库环境下如何设定快捷键

如何在dra建库环境下如何设定快捷键

-

2018-07-30

如何设定建库的环境为MM公制单位

如何设定建库的环境为MM公制单位

-

2018-07-30

如何设定建库的环境为MIL英制单位

如何设定建库的环境为MIL英制单位

-

2018-07-30

实现焊盘标准化为满足YEPEDA焊盘命名规范和焊盘设计规范的焊盘

实现焊盘标准化为满足YEPEDA焊盘命名规范和焊盘设计规范的焊盘

-

2018-07-30

自动创建各类标准焊盘

自动创建各类标准焊盘

-

2018-07-30

如何导出选择的单个或者多个焊盘到用户指定的目录

如何导出选择的单个或者多个焊盘到用户指定的目录

-

2018-07-30

重新批量命名封装的pinnumber

重新批量命名封装的pinnumber

-

2018-07-30

全自动创建规则性封装

全自动创建规则性封装

-

2018-07-30

半自动化创建封装库辅助工具

半自动化创建封装库辅助工具

-

2018-07-30

查找在多个库路径下的封装

查找在多个库路径下的封装

-

2018-07-30

查在单个库路径下的封装

查在单个库路径下的封装

-

2018-07-30

如何实现Allegro封装版本降级

如何实现Allegro封装版本降级

-

2018-07-30

批量增加封装库的属性信息

批量增加封装库的属性信息

-

2018-07-30

简易计算器

简易计算器

-

2018-07-30

批量将symbol文件(*.dra)生成为device文件

批量将symbol文件(*.dra)生成为device文件

-

2018-07-19

YepChecker工具功能介绍

YepChecker工具功能介绍

-

2018-07-19

DRC定位工具

DRC定位工具

-

2018-07-19

清除设计图上的审核程序YepChecker生成的DRC标识

清除设计图上的审核程序YepChecker生成的DRC标识

-

2018-07-19

审核器件为何无法正常摆出

审核器件为何无法正常摆出

-

2018-07-18

检查器件的REF是否被误删除

检查器件的REF是否被误删除

YepStudyV2.0.rar

YepStudyV2.0.rar